Novel Computing Technologies

Welcome to the Novel Computing Technologies group at ZITI.

Our group is kindly supported by Carl-Zeiss-Stiftung and Google.

We research non-traditional ways of computing, including non von Neumann Computing systems and Reprogrammable Hardware (FPGAs and others). We are building computing chip using new technologies, such as ReRAM (memristor) FPGAs Build holistic solutions for end-to-end frameworks for (e)FPGA development, partial reconfiguration implementation tools and the corresponding middleware (FOS – the FPGA Operating System) We also work on security and reliability in reconfigurable systems.

Some of our main projects and research directions:

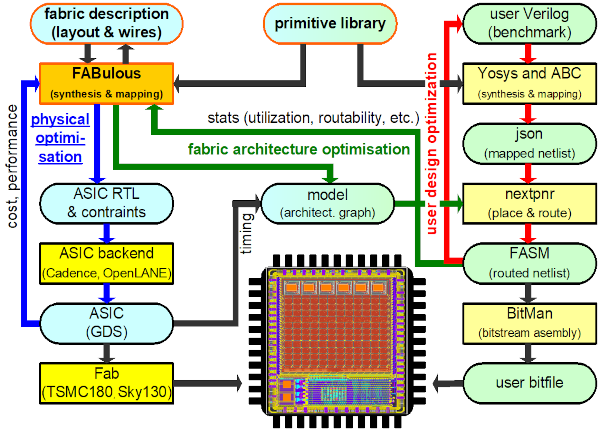

The FABulous open (e)FPGA framework

FABulous deals with the ASIC generation (RTL code & constraints generation) and it supports custom primitives (e.g., pass-gate muxes).

We achieve high quality of results (>90% core utilization) and aresilicon-proven on TSMC 180 and Skywater 130 processes. FABulous is very versatile with respect to the fabric parameters (size, logic, DSP, memory blocks) and the IPs integrated (e.g., RISC-V) as well as supporting different technology options such as non-volatile ReRAM (memristor) variants. Its currently the only open-source FPGA framework supporting partial reconfiguration.

Furthermore, FABulous can parameterize open-source FPGA CAD tools (Yosys, nextpnr, VPR) for the RTL to bitstream compilation and we have simulation (Verilator) and emulation options (using Xilinx/AMD or Intel FPGAs).

Diagram of the FABulous workflow.

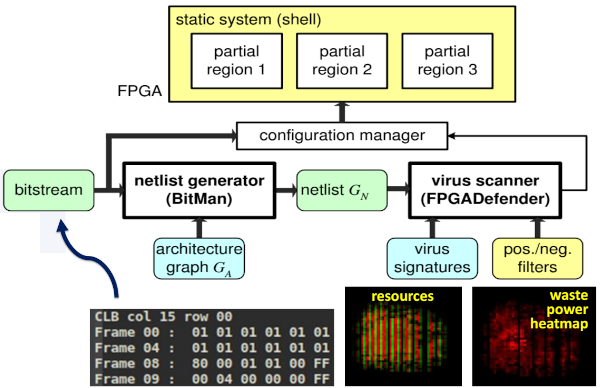

The FPGADefender FPGA Bitstream Virus Scanner

Low-level FPGA programmability is a huge security threat!

The theoretical power-hammering potential of a datacenter FPGA is ~10KW (and we have demonstrated crashing of AWS instances by deploing just 300W)

For protecting against this, we are building a sophisticated security ecosystem providing:

- Bitstreams analysis to detect:

- short circuits,

- high fan-out nets

- wire tapping

- glitching

- module bounding boxes

- high fanout nets

- Runtime monitoring (e.g., power) and encapsulation (OS-services for FPGAs)

- FPGA health checking (detect aging and defects early)

The FPGADefender virus scanner works directly at the bitstream level to provide maximum confidence.

Dynamically Reconfigurable Systems

We have built an entire ecosystem for dynamically reconfigurable systems consisting of: design tools (GoAhead, BitMan), infrastructure (e.g., different shells for embedded systems and datacenters) and middleware & drivers for FPGA virtualization (FOS). We support multi-tenancy (run multiple users/applications simultaneously) memory and performance aware scheduling (space & time) and dynamic stream processing (runtime module stitching). We used that in multi-FPGA platforms (relocate bitstreams across FPGAs) as well as in video processing, ML and database acceleration systems.

GoAhead tool

We developed the GoAhead tool for implementing partially reconfigurable systems. With GoAhead. modules can be relocated across the chip, instantiated multiple times and even be reused in different systems (as long that uses the same FPGA familiy). Reconfigurable modules can connect in a streaming mode for implementing stitchable pipelines (directly from relocatable bitstreams) GoAhead supports most Xilinx FPGAs, including latest UltraScale devices.

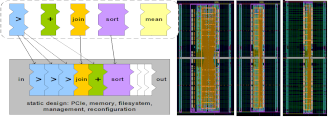

Dynamic stream processing

Dynamic stream processing: composing optimized accelerator pipelines for problems only known at runtime. This is useful for applications like signal processing, video and database acceleration (as in the figure). For the latter we stitch modules together according to the present query, but also taking into account the available resources such that we get the entire fastest possible execution time.

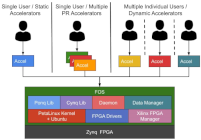

FOS - The FPGA Operating System

For managing partially reconfigurable systems and for virtualizing the FPGA, (multiple) users or applications can request acceleration services (rather than just accelerators), and FOS will manage configuration and execution such that overall performance is improved. All FPGA low-level management, bitstream manipulation and memory management is done automatically by FOS.

Resource-elastic Hardware

FOS implements the concept of resource-elastic hardware where a system adapts to runtime conditions such as requested work and currently available resources. Compared to standard approaches (a) our resource-elastic scheduler can expand and shrink resource allocation for individul acceleration services (b) that is entirely transparent for the rest of the system. This provides faster operation particularly in dynamic workload scenarios.

Student Projects

For student projects (including BSc and MSc) have a look at our projects list or contact dirk.koch@ziti.uni-heidelberg.de